# SocTek® IP Cores

10M/100M/1G/10G Managed/Unmanaged

(TSN) Ethernet Switch IP Core

TGES

# 概要

TGES は、Time-Sensitive Networking (TSN) 機能を備えたマルチポート、マルチレートの管理型イーサネット スイッチです。

内部マイクロアーキテクチャには、重要なユースケースでもスイッチの信頼性の高い動作を保証するための革新的な機能強化が含まれています。

TGES には、特定のユーザーのニーズに応じてロジックリソースフットプリントを最適化するために、合成時と実行時の両方で構成可能な豊富なパラメータ セットがあります。これらのジェネリックは、Vivado GUI を介してグラフィカルに構成することもできます。

これらすべての特性により、TGES IP コアの使用が鍵となるさまざまなアプリケーション/セクターが可能になります。自動車、海洋、航空宇宙、防衛、電気などは、当社のお客様がすでにこのテクノロジーを適用している市場の例です。

## 主な特徴

- Time-Sensitive Networking (TSN) サポート: 航空宇宙 (P802.1DP)、自動車 (P802.1DG)、産業オートメーション (IEC/IEEE 60802) などのさまざまな TSN プロファイルに準拠しています。

- Ethernet Switch IP “builder”: 数百のユーザー設定可能なパラメータにより、顧客が必要とする正確なスイッチ設定を取得でき、利用可能なプログラマブル ロジックリソースを効率的に使用できます。

- ポートごとに異なるデータレート: 各ポートの速度とインターフェースを個別に割り当てることができます。

- 高性能: HOL (ヘッドオブライン) ブロッキング効果のない最大 10G インターフェース。

- 高速かつスムーズな統合: 一部のFPGAベンダツール (AMD Vivado™ Design Suite など) で GUI が利用可能。ドライバとソフトウェアコンポーネントは製品の一部として含まれています。

- 評価版: 暗号化された期間限定版あり。

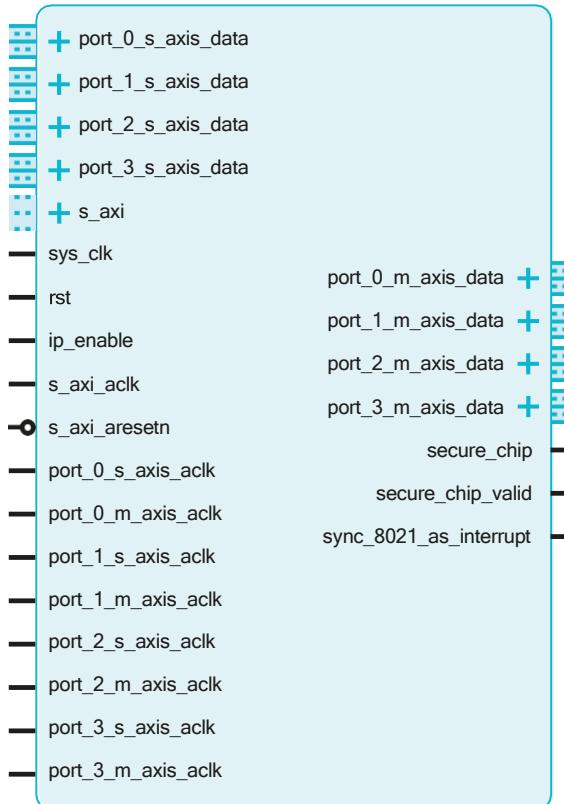

## GUIブロック図

# 技術仕様

## 通信インターフェース

- 10/100 Mbps および1Gbps PHYインターフェースレート用の統合型

10M/100M/1000M MAC により、アプリケーションに応じて任意のPHYインターフェースタイプ (MII、GMII、RGMII など) で使用可能

- AMD LogiCORE™ SGMII IP コアおよびLogiCORE™ QSGMII IP コアへの内部 GMII ベース接続を通じて、SGMII (シリアル ギガビット メディア独立インターフェース) または QSGMII (クアッド シリアル ギガビット メディア 独立インターフェース) PHYインターフェースと互換性あり

- 複数のデータレートをサポートする構成可能な AXI-Stream インターフェース:

- 125MHzでデータ幅8 ビットの10/100/1000 Mbps AXI-Sインターフェース

- 312.5 MHz でデータ幅 32 ビットの 10/100/1000/2500/5000/10000 Mbps AXI-S インターフェース

- データ幅64 ビット@156.25 MHz 10/100/1000/2500/5000/10000 Mbps AXI-Sインターフェース

- AMD LogiCORE™ USXGMII IPコアおよびLogiCORE™ 10G/25G Ethernet Subsystem IPコアへの内部AXI-Sベース接続を通じて、USXGMII (Universal Serial 10GE Media Independent Interface) または10GBASE-R PHYインターフェースと互換性あり

## Time-Sensitive Networking (TSN)

- TSN機能は独立して有効/無効にできる

- IEEE 802.1AS - Timing and Synchronization

- IEEE 802.1Qav - クレジットベースシェーバー(Credit Based Shape: CBS)

- IEEE 802.1Qbv - 時間認識シェーバー-Time Aware Shaper (TAS)

- IEEE 802.1Qci - ストリームごとのフィルタリングとポリシング

- IEEE 802.1CB - フレーム複製と排除による信頼性 (Frame Replication and Elimination for Reliability: FRER)

- IEEE 802.1Qcc - ストリーム予約プロトコル (Stream Reservation Protocol: SRP) の強化と性能向上

## Time Synchronization

- IEEE 802.1AS-2020およびIEEE1588 (PTP) に準拠した時間同期

- 最大4つのIEEE 802.1AS時間ドメイン

- レガシー PTP: レイヤー 2 およびレイヤー 3 (IPv4 および IPv6) での IEEE1588 透過

- クロック (TC) 機能 (エンドツーエンドまたはピアツーピア)

- レガシー PTP: レイヤー 2 およびレイヤー 3 (IPv4 および IPv6) での IEEE 1588 境界クロック (BC)

## Traffic Management

- 最大 32 個のポートをサポートする統合イーサネットスイッチファブリック (デバイスの利用可能なリソースによって数が制限されます)

- HoLB (Head of Line Blocking) フリースイッチファブリック

- HoLB効果を防ぐためのVOQ (Virtual Output Queue) ベースのフレームストレージパフォーマンスを犠牲にすることなくリソース使用量を削減するための最適な内部アーキテクチャを定義するリソース共有アルゴリズム (合成時に実行)

- 共有の動的および静的フィルタリングデータベース。最大9Kの絶対MACアドレス (合成スケーラブル) のハードウェアMACアドレスラーニング/エージングと検索をワイヤスピードで実装

- MACアドレス学習のための独立したVLAN学習サポート

- フィルタリングデータベースに含まれる検索可能なMACアドレス (および関連情報)

- ポートへのフレーム転送を制限するためのプログラム可能なフレーム転送ポートマスク

- 静的マルチキャストフレームフィルタリング

- マルチキャストフレームフィルタリングのためのIGMP v1/v2スヌーピング1 (IPv4) サポート

- 標準フレームサイズのサポート(1518)または最大9kByte のジャンボフレーム (メモリの可用性に依存)

## Quality of Service

- ポートあたり最大8つの優先キュー（合成オプション）

- PCP ビットに基づく優先度分類（802.1p）

- 厳密な優先スケジューリングアルゴリズムに基づく出力トラフィックの優先順位付け

- IEEE 802.1Q タグベースおよびポートベースの VLAN。受信 (VLAN 挿入) および送信 (VLAN 削除/上書き) における VLAN 操作機能

## Network Management & Monitoring

- IEEE 802.1D Spanning-Tree Protocol (STP) スイッチまたはブリッジが複数のパスを介して相互接続されている場合、ループが形成されるのを防ぎます

- IEEE 802.1w Rapid Spanning Tree Protocol (RSTP) は、Spanning-Tree の高速収束を実現します

- IEEE 802.1s マルチスパンニングツリープrotocol (MSTP) は、複数のSpanning-Treeを許可することで、複数のVLAN環境でリンクの可用性を実現します

- ポートミラーリング機能。フレームをミラーポートにコピーできるようにする入力および出力ミラーリング機能。特定のデータパターンに一致するフィルタリングされたフレームのみをミラーリングするオプション

- 管理およびデバッグ用のポートごとのMACおよびスイッチ統計

- 制御レジスタと統計レジスタにアクセスするための幅広い管理インターフェース（合成時に選択可能）

- 外部デバイス構成用のI2Cマスターインターフェース（不揮発性構成のEEPROMメモリなど）

## その他

- Distributed Switch Architecture (DSA) フレームタグ付けにより、アプリケーション固有のメッセージを管理ポートにマージし、アプリケーション固有のメッセージを特定のポートに配信します

- 管理ポートとの間で既知のプロトコル固有のフレームまたはカスタムフレームを排他的に転送

## 技術サポート、検証および納品物

### 技術サポート

IP ライセンスは、当社の経験豊富なサポートエンジニアとの直接のコミュニケーションチャネルを確保する技術サポートパッケージとともに提供されます。

これは、顧客の製品開発および統合フェーズで非常に役立ちます。

### 検証

当社のすべてのIPコアは、厳密にテストされ、ハードウェアで検証され、実際の環境で確認されています。IP製品の検証には3段階のプロセスが適用されます：

- エンティティ/ブロック指向のシミュレーション

- グローバル指向のシミュレーション

- ハードウェアでの検証

## 納品物

- 暗号化されたソースRTLコード

- ソフトウェアコンポーネント：ドライバ、設定API、ソフトウェアスタック

- ドキュメント（IPコアおよびソフトウェアコンポーネント）

- （オプション） Networking Testbench Suite NTS

- （オプション） AMD Vivado™設計スイートのサンプル設計

## 関連製品

- Networking Testbench Suite (NTS)

- TSN EndPoint (ETSN IP Core)

- 1G TSN イーサネットスイッチ (MTSN IP Core)

- 1G Managed イーサネットスイッチ (MES IP Core)

## Ordering Code

### Ordering code

S-3135 (TGES IP Core)

他の利用可能な参照について詳しく知りたい場合は、担当の営業担当者にお問い合わせください。

# SocTek® By

TGES

10M/100M/1G/10G Managed/Unmanaged

(TSN) Ethernet Switch IP Core

# SOC-E®

[www.sherpa-tech.jp/tsn\\_solutions](http://www.sherpa-tech.jp/tsn_solutions)

info@sherpa-tech.jp

株式会社シェルバ

〒222-0033 神奈川県横浜市港北区新横浜2-5-4 京浜建物第2ビル 801号室

TEL : 045-475-2701 FAX : 045-475-2702