# SocTek® IP Cores

100M/1G/10G

TSN Endpoint IP Core

ETSN

## 概要

ETSN (End System Time-Sensitive Networking) は、ネットワーク内でエンドシステムとして機能するデバイスにTSN (Time-Sensitive Networking) の機能を提供します。エンドシステムは通常、ネットワーク内で交換されるデータの送信元 (talker) や受信先 (listener) として動作します。

内部のマイクロアーキテクチャには、クリティカルなユースケースでもエンドポイントの信頼性の高い動作を確保するための革新的な機能強化が含まれています。

ETSNは、レイヤー2の豊富な設定可能な機能を持ち、設計時（合成時）と実行時に両方で利用可能です。これにより、TSN機能を備えた高度なエンドシステムを構築できます。ETSNスイッチは、最適化されたリソースを使用して最大スループットを実現するよう設計されています。

これらすべての特性により、ETSN IP コアの使用が鍵となるさまざまなアプリケーション/セクターが可能になります。自動車、海洋、航空宇宙、防衛、電気などは、当社のお客様がすでにこのテクノロジーを適用している市場の例です。

## 主な特徴

- Time-Sensitive Networking (TSN) サポート: 航空宇宙 (P802.1DP)、自動車 (P802.1DG)、産業オートメーション (IEC/IEEE 60802) などのさまざまな TSN プロファイルに準拠しています。

- IP “builder”: 数百のユーザー設定可能なパラメータにより、顧客が必要とする正確な設定が可能になり、利用可能なプログラマブルロジックリソースを効率的に使用できるようになります。

- 高速かつスムーズな統合: 一部の FPGA ベンダー ツール (AMD Vivado™ Design Suite など) で GUI が利用可能。ドライバとソフトウェア コンポーネントは製品の一部として含まれています。

- 評価版: 暗号化された期間限定版あり。

# 技術仕様

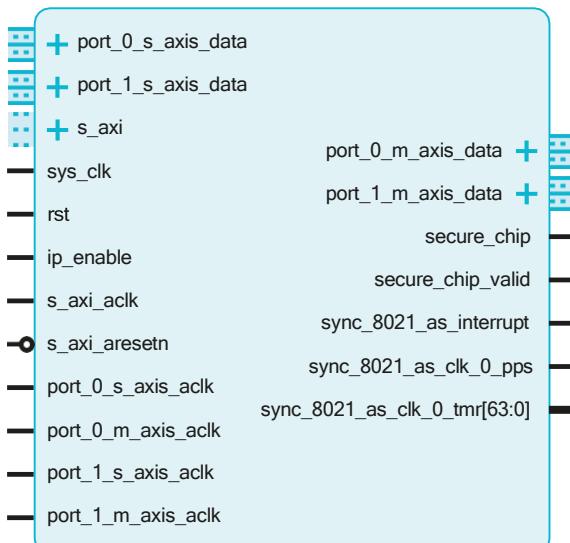

## 通信インターフェース

- 10/100 Mbps および 1 Gbps PHY インターフェース レートに対応する統合 10M/100M/1000M MAC を搭載し、アプリケーションに応じて任意の PHY インターフェース タイプ (MII、GMII、RGMII など)で使用可能

- AMD LogiCORE™ SGMII IPコアおよび LogiCORE™ QSGMII IPコアへの内部 GMIIベースの接続を通じて、SGMII（シリアルギガビットメディア独立インターフェース）または QSGMII（クアッドシリアルギガビットメディア独立インターフェース）PHYインターフェースと互換性があります。

- 複数のデータ レートをサポートする設定可能な AXI-Stream インターフェース:

- 10/100/1000 Mbps AXI-Sインターフェース、データ幅8ビット@125 MHz

- 10/100/1000/2500/5000/10000 Mbps AXI-S インターフェース、データ幅 32 ビット @ 312.5 MHz

- 10/100/1000/2500/5000/10000 Mbps AXI-S インターフェース、データ幅 64 ビット @ 156.25 MHz

- AMD LogiCORE™ USXGMII IPコアおよび LogiCORE™ 10G/25G Ethernet Subsystem IPコアへの内部AXI-Sベース接続を通じて、USXGMII（ユニバーサルシリアル 10GEメディア独立インターフェース）または 10GBASE-R PHYインターフェースと互換性があります。

## Time-Sensitive Networking (TSN)

- TSN機能は独立して有効/無効にできる

- IEEE 802.1AS - Timing and Synchronization (gPTP)

- IEEE 802.1Qav - クレジットベースシェーバー (Credit Based Shape: CBS)

- IEEE 802.1Qbv - 時間認識シェーバー (Time Aware Shaper:TAS)

- IEEE 802.1Qci - ストリームごとのフィルタリングと ポリシング (Per-Stream Filtering and Policing:PSFP)

- IEEE 802.1CB - フレーム複製と排除による 信頼性 (Frame Replication and Elimination for Reliability:FRER)

- IEEE 802.1Qcc - ストリーム予約プロトコル (Stream Reservation Protocol:SRP) の強化と性能向上

## Time Synchronization

- IEEE 802.1AS-2020 (gPTP) および IEEE 1588 (PTP) による時刻同期

- 最大4つの IEEE 802.1AS タイム ドメイン

- レガシー PTP: IEEE 1588 Transparent Clock(TC) 機能 (エンド・ツー・エンドまたはピア・ツー・ピア) で レイヤー2およびレイヤー3 (IPv4) 対応

- レガシー PTP: IEEE 1588 バウンダリークロック (BC) 機能でレイヤー2およびレイヤー3 (IPv4) 対応

## Traffic Management

- リソース共有アルゴリズム（合成時に実行）：パフォーマンスを損なうことなく、リソース使用を削減するための最適な内部アーキテクチャを定義

- 動的および静的フィルタリングデータベースの 共有：最大9Kの絶対MACアドレスのハードウェアMACアドレsslーニング／エイジング ヒルックアップをワイヤースピードで実行（合成スケーラブル）

- 独立したVLAN学習のサポート：MACアドレス学習のサポート

- フィルタリングデータベースに含まれる検索可能なMACアドレス（および関連情報）

- 静的マルチキャストフレームフィルタリング

- IGMP v1/v2スヌーピング（IPv4）：マルチキャストフレームフィルタリングのサポート

- 標準フレームサイズ（1518バイト）または 最大9KBのジャムボフレーム（メモリの可用性による）

## Quality of Service

- ポートごとに最大8つの優先度キュー（合成オプション）

- 優先度分類は、PCPビット（802.1p）、IPパケットのDSCP TOSビット（IPv4 TOS / IPv6 COS）、およびEtherTypeに基づく

- PCPまたはDSCPフィールドから内部優先度キューへのリマッピングをポート単位でプログラム可能

- ポート単位での優先度再生成が可能

- 送信トラフィックの優先度付けは、厳密な優先度または加重ラウンドロビン（WRR）スケジューリングアルゴリズムに基づく

- IEEE 802.1QタグベースおよびポートベースのVLAN：受信時のVLAN操作（VLAN挿入）

- および送信時のVLAN操作（VLAN削除／上書き）

- 宛先MACアドレスおよび／またはEtherTypeに基づくポート単位でMACレベルの入力フレームフィルタリング

- ポート単位でトーケンバケットベースの入力スループット制限

- ポート単位でMACレベルの出力スループット制限

- ポート単位でMACレベルの出力フレームレート制限

- 送信フレームレート制限：ポート単位でブロードキャスト／マルチキャストストーム保護

## Network Management & Monitoring

- IEEE 802.1D スパニングツリープロトコル（STP）：スイッチやブリッジが複数のパスで相互接続される際に、ループが形成されるのを防止

- IEEE 802.1w ラピッドスパニングツリープロトコル（RSTP）：スパニングツリーの急速な収束を提供

- IEEE 802.1s マルチプルスパニングツリープロトコル（MSTP）：複数のスパニングツリーを許可することで、複数のVLAN環境でのリンクの可用性を提供

- ポートミラーリング機能：イングレスおよびイーグレスのミラーリング機能により、フレームをミラーポートにコピー可能。特定のデータパターンに一致するフィルタリングされたフレームのみをミラーリングするオプション

- ポートごとのMACおよびスイッチ統計：管理およびデバッグの目的で使用

- 広範な管理インターフェース：アクセス制御および統計レジスタにアクセスするためのインターフェース（合成時に選択可能）

## その他

- Distributed Switch Architecture (DSA) フレームタグ付け：アプリケーション固有のメッセージを管理ポートに統合し、特定のポートにアプリケーション固有のメッセージを配信

- 管理ポートへの/からの既知のプロトコル固有フレームやカスタムフレームの排他的転送

# 技術サポート、検証および納品物

## 技術サポート

IP ライセンスは、当社の経験豊富なサポートエンジニアとの直接のコミュニケーションチャネルを確保する技術サポートパッケージとともに提供されます。

これは、顧客の製品開発および統合フェーズで非常に役立ちます。

## 検証

当社のすべてのIPコアは、厳密にテストされ、ハードウェアで検証され、実際の環境で確認されています。IP製品の検証には3段階のプロセスが適用されます：

- エンティティ/ブロック指向のシミュレーション

- グローバル指向のシミュレーション

- ハードウェアでの検証

## 納品物

- 暗号化された/ソースRTLコード

- ソフトウェアコンポーネント：ドライバ、設定API、ソフトウェアスタック

- ドキュメント（IPコアおよびソフトウェアコンポーネント）

- （オプション） Networking Testbench Suite (NTS)

- （オプション） AMD Vivado™設計スイートのサンプル設計

## 関連製品

- Networking Testbench Suite (NTS)

- 1G TSNイーサネットスイッチ (MTSN IPコア)

- 10G TSNイーサネットスイッチ (TGES IPコア)

## Ordering Code

### Ordering code

S-3139 (ETSN IP Core)

他の利用可能な参照について詳しく知りたい場合は、担当の営業担当者にお問い合わせください。

# SocTek® By

ETSN

100M/1G/10G

TSN Endpoint IP Core

# SOC-E®

[www.sherpa-tech.jp/tsn\\_solutions](http://www.sherpa-tech.jp/tsn_solutions)

info@sherpa-tech.jp

株式会社シェルバ

〒222-0033 神奈川県横浜市港北区新横浜2-5-4 京浜建物第2ビル 801号室

TEL : 045-475-2701 FAX : 045-475-2702